百度翻译: 划词翻译做的很认真呢

在繁忙的数字时代,翻译工具已成为人们沟通与学习的得力助手。而在众多选择中,百度翻译以其细致入微的划词翻译功能悄然引起了广泛关注。它像一位专注的助手,认真对待每一次词句的转换,努力将复杂的语言变得触手可及。本文将带你深入探讨百度翻译的划词翻译,为何它能在众多工具中脱颖而出,彰显出一份难得的用心与专业。

百度翻译的细节打磨:提升划词体验的幕后功夫

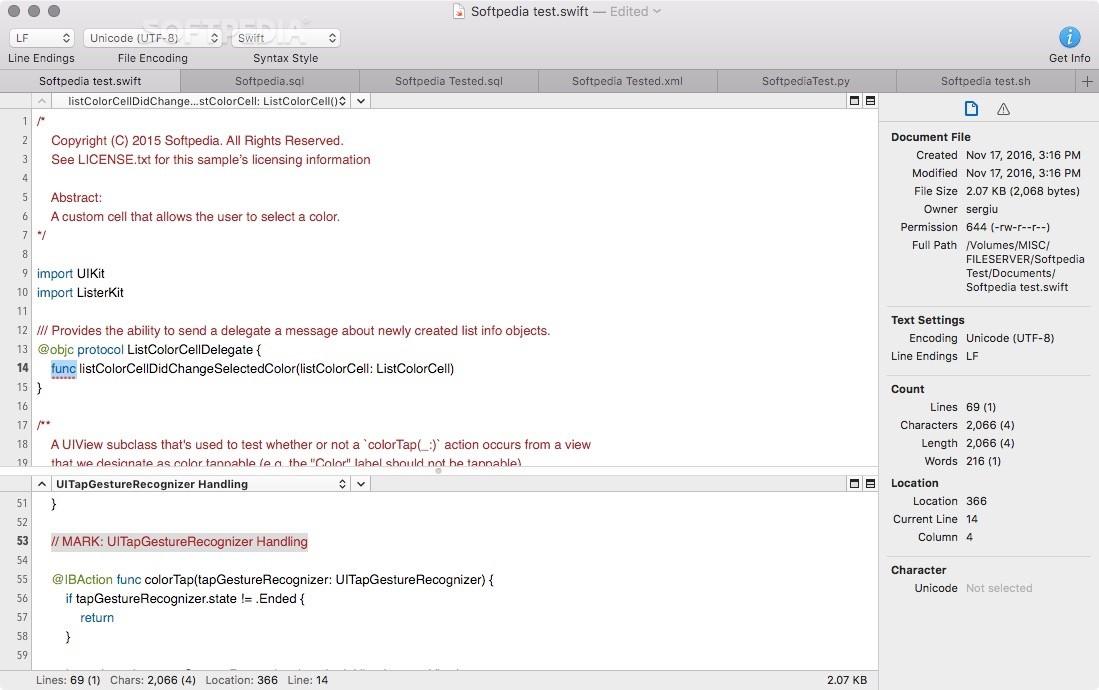

百度翻译在划词体验的细节打磨上展现出极高的用心。从字体的选用到交互的流畅,每一个环节都经过反复雕琢。精细的气泡提示确保用户在悬停或点击时能够快速获取信息,避免繁琐的操作步骤。同时,界面布局采用简洁而直观的设计,让用户在使用过程中犹如与一位贴心的翻译助理对话,减少了使用门槛。

为了提升整体体验,百度翻译还优化了多语言支持和划词范围的精准度。在细节部分,比如在不同操作系统或浏览器中的兼容性测试,以及根据用户反馈持续调整交互的细节。例如,以下表格展示了这些努力的成果:

| 细节优化点 | 成果表现 |

|---|---|

| 悬浮提示的延迟时间 | 极致流畅,没有卡顿 |

| 多语言界面切换 | 无缝体验,支持多设备 |

| 划词范围智能识别 | 准确率提升,理解更细腻 |

智能化识别与精准释义的完美结合

在现代翻译技术中,智能化识别引领着语言转换的新潮流。百度翻译通过深度学习算法,精准捕捉用户划词选择的语境,从而实现高效的内容识别。这种技术不仅提升了翻译的速度,更确保每一次划词都得到最贴切的释义,让用户在阅读和理解中感受到科技的细腻关怀。

与此同时,释义的精准也体现了技术的用心,包括多义词、专业术语的智能区分,确保每个词在不同情境下都能获得恰当的解释。以下是百度翻译在识别与释义上的几大亮点:

- 智能识别复杂句结构,快速定位关键词

- 多维释义,满足不同专业领域的翻译需求

- 场景匹配,准确还原语境意图

技术对比表

| 特性 | 百度翻译 | 传统工具 |

|---|---|---|

| 识别能力 | 智能检测语境 | 依赖关键词匹配 |

| 释义精准度 | 多层次多义释义 | 单一释义 |

Sponsor

百度翻译在划词翻译功能上的精雕细琢,不仅仅是技术层面的突破,更是对语言理解深度的一次飞跃。它犹如一位深谙用户心思的语言大师,在用户指尖轻划的瞬间,便能精准捕捉其意图,并提供多维度的释义。这种智能化识别如同拥有了“火眼金睛”,能够穿透语言表面的迷雾,直达语义的核心。

而精准释义则像是将多语种的文化内涵融会贯通。它不仅仅是简单的字面翻译,更是对词语在特定语境下的细微差别的深刻理解。无论是专业术语、俚语俗语,还是网络热词,百度翻译都能给出令人满意的答案。这种完美的结合,让用户在跨语言交流中如鱼得水,轻松驾驭各种语言环境。

以下是一些百度翻译在智能化识别与精准释义方面体现的细节:

能够识别不同领域的专业术语,并给出相应的解释。

针对俚语俗语,提供地道的翻译和文化背景说明。

对网络热词的翻译紧跟时代潮流,避免翻译的滞后性。

场景

用户输入

百度翻译的智能回应

学术论文

"Quantum entanglement"

提供量子纠缠的学术定义和相关研究资料链接。

日常口语

"Hangry"

解释为“饿怒”,并给出类似的口语表达。

网络用语

"YYDS"

识别为“永远的神”,并解释其在网络语境下的含义。

Want to create your own content like this? Check out Article Generation.Get 2,000-word SEO-optimized articles instantly and save over $2,500 a month!

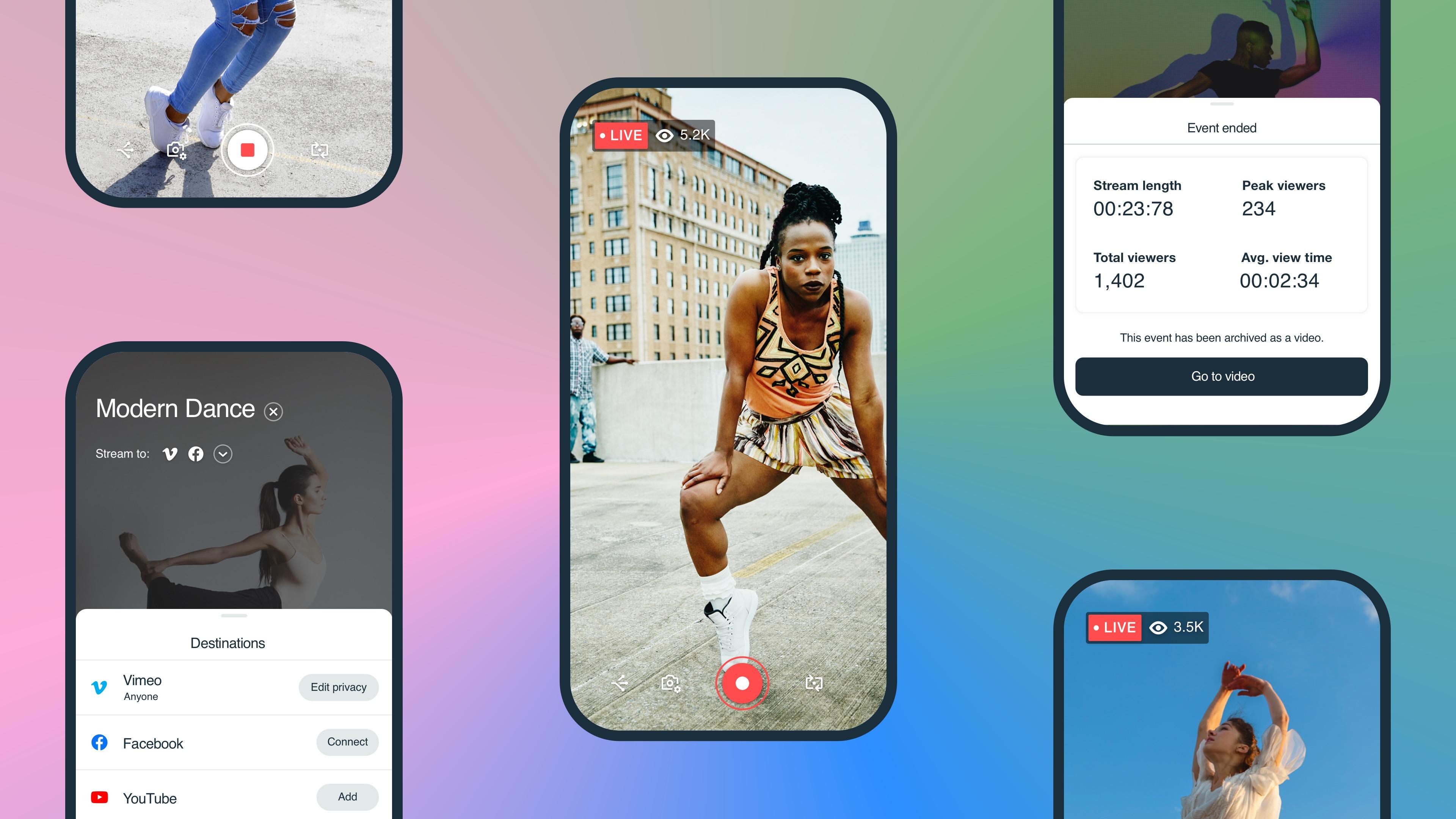

用户体验优化:让划词翻译更加顺畅自然

为了让用户在使用划词翻译时体验更加顺畅自然,系统在界面设计与交互逻辑上进行了全面优化。高效的响应速度,确保在轻轻一划后,翻译结果即刻呈现,无需等待。与此同时,自动识别多语言环境,大大减少用户手动切换的繁琐步骤,让多语切换变得无缝顺畅。此外,采用智能预加载技术,提前加载可能的翻译内容,为用户带来几乎无感的操作体验。

在用户体验方面,细节设计也尤为重要。例如,优化的UI布局让划词区域更宽敞、操作更直观,提示气泡采用柔和色调,轻轻一触便能获得丰富信息。以下是一些核心优化点:

- 快速响应的翻译建议

- 无干扰的界面设计

- 多设备无缝同步体验

| 优化特色 | 用户享受 |

|---|---|

| 一触即达 | 快速翻译,减少等待 |

| 智能识别 | 自动识别多语言切换 |

| 无缝体验 | 跨设备同步操作 |

未来发展方向:不断突破的翻译创新之路

在不断推进的翻译创新道路上,百度翻译正积极融合人工智能与自然语言处理技术,探索更加智能化和个性化的翻译体验。未来,技术突破将带来更高的翻译准确率和更自然的表达方式,使用户在跨语言沟通中感受到前所未有的便捷与流畅。创新不仅限于工具层面,更涵盖用户交互、内容理解与多模态融合,真正实现“懂你所需,表达得体”。

此外,未来的发展方向还包括打造开放式生态系统,激励全球开发者和内容创造者共同参与到翻译技术的创新实践中。 通过引入AI学习与云端大数据,百度翻译将持续优化其算法模型,力求在多语言、多场景中表现出更强的适应性与智能化。

未来发展重点:

- 增强语境理解能力,让翻译更贴合实际情境

- 结合多模态数据实现跨媒体翻译

- 推动行业应用与本地化服务的深度融合

| 关键词 | 目标 | 技术支撑 |

|---|---|---|

| 智能理解 | 深度理解语境 | 自然语言处理 |

| 多模态融合 | 跨媒介翻译 | 计算机视觉 & 语音识别 |

| 生态合作 | 共建创新平台 | 开放API & SDK |

To Wrap It Up

在这片纷繁复杂的语言海洋中,百度翻译以其细腻的划词识别功能,为我们搭建了一座桥梁。它用心的每一次划选,仿佛在静静讲述一个关于理解与沟通的故事。未来,随着技术的不断革新,或许我们即将迎来更加智能、更加贴心的翻译助手,让世界的每一个角落都能无障碍地交流与碰撞。让我们拭目以待,继续见证科技带来的精彩变化。